期待のネット新技術

NVIDIAのGPU間データ伝送技術「NVLink」に見る、電気→光の移行が一筋縄では行かない例

Silicon Opticsの現状(7)

2025年10月7日 06:00

TSMCについて前々回および前回の2回で取り上げたのは、NVIDIAが採用を発表した「COUPE」の開発元としてであった。今回は、NVIDIAのNVLinkの話をご紹介したい。

まず最初にお断りすると、NVIDIAの現在の計画では、直近のNVLink 5やNVLink 6をOpticalに切り替える予定はなく、銅配線のまま頑張る、と表明している。「タイトル詐欺じゃないか」と言われそうだが、「現在の計画」であることに注意してほしい。つまり以前はOpticalへの移行を真剣に考えていたのである。というか、今も考えてはいるのだろうが、EthernetやInfinibandと異なり、まだCrossoverの時期ではないと判断した、というのが正確だろうか。

2022年にはNVLinkのOptical化が検討されていた

まず、以前の話をちょっとご紹介する。ここからのスライドはHot Interconnects 2023の初日に行われた、NVIDIAのBill Dally博士(SVP Research&Chief Scientist兼スタンフォード大教授)による"Accelerator Clusters:the New Supercomputer"からのものだが、実はOFC 2022においても博士はほぼ同様の講演を行っており(この時のスライドはThe Next Platformのこちらの記事で確認できる)、2022年時点でもうNVLinkのOptical化を真剣に検討していたことが分かる。

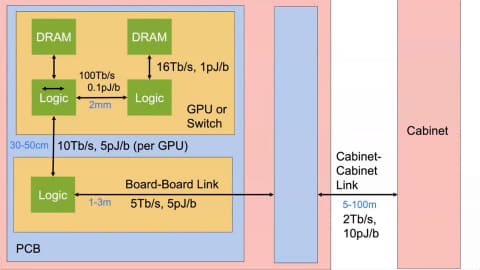

さて、まずは基礎である(図01)。

GPUカードとNetwork Cardがマザーボード上に搭載され、そこからTOR Switchを経由して別のキャビネットにあるSwitchに繋がるといったケースでの距離と帯域、消費電力をまとめたものだ。これは全部銅配線、つまり電気信号ベースでの数字である。ただし電気信号の場合、いろいろな限界が存在する、というのが図02だ。。

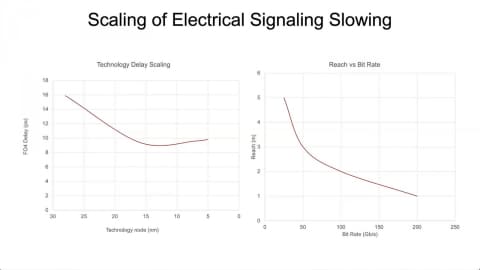

右はプロセスノードとLatencyの関係で、プロセスを微細化すると高速化とか高密度化、低消費電力化が期待できる(これも無条件で期待できたのは130nmくらいの世代までの話で、その後はむしろ消費電力が急増する一方であり、これをさまざまな新技術で克服して何とか低消費電力に抑えているというのが正確なところだが、それはそれとして)一方、Latencyそのものは14nm世代あたりで底を打ってやや増加傾向にあるとする。

また、右の距離とBit Rateの関係は何度か出てきた話で、到達距離を伸ばそうとするとBit Rateはどうしても低くなるし、逆にBit Rateを上げようとすると到達距離は減る。グラフでは1mで200Gbpsが実現可能としているが、これは現在IEEE P802.3dj Task Forceで検討中の200GBASE-CR1/400GBASE-CR2/800GBASE-CR4を指してのことと思われる。

余談だが、IEEE P802.3djはすでにTask ForceでのReviewを終了し、現在はWorking Group Ballotの段階になっている。ただ現在のTimelineだと標準化が完了するのは2026年9月頃と、まだ1年ほど掛かりそうだ。

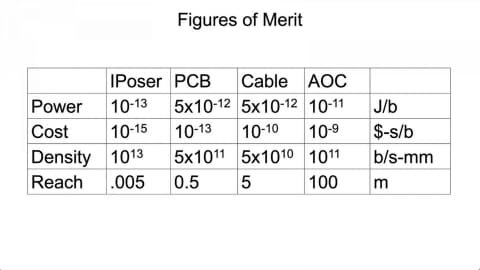

話を戻すと、Interposer(チップ同士の接続に利用するもの)/PCB(マザーボードとかGPUカードなどの基板)/Cable(銅ケーブル)/AOC(Active Optical Cable:光ケーブル)でのそれぞれの得失をまとめたのが図03であるが、現時点ではAOCは一番コスト面で不利であり、また消費電力も決して良いとは言えない。

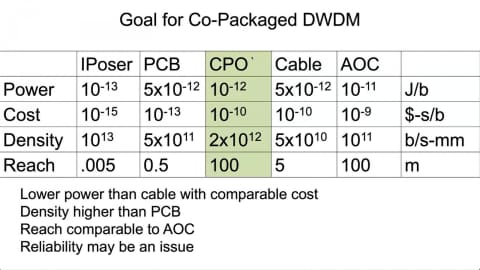

まぁこれはAOCだからで、Passive Optical Cableならもう少しマシにはなると思うのだが、今のところ他と比べて明確に有利なのは到達距離だけである。ただここでDWDMを併用したCPOを利用した場合、問題が大幅に改善して現実的な選択肢になる、と主張する(図04)。

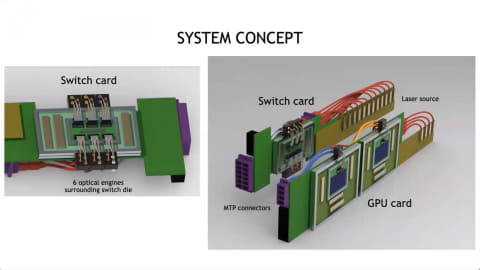

コストは銅ケーブルと同等まで落ち、帯域は銅ケーブルより遥かに大きく、それでいて消費電力も下がることから、途端に魅力的な選択肢になり得るというわけだ(もちろん、信頼性というかBERに関しては検討の余地があるのだが)。では、実際にそれをGPUとかSwitchに実装する場合どうなるか? というコンセプトが図05となる。

あくまでもコンセプトではあるのだろうが、なかなか無茶な構成ではある。PIC/EICをGPU/Switchのそばに配し、間を空中配線で繋ぐというのは量産ではありえない構成ではある。今ならEIC/PICのダイとGPU/Switchのダイを同じパッケージに収め、間をInterposerでつなぐ形になるだろう。

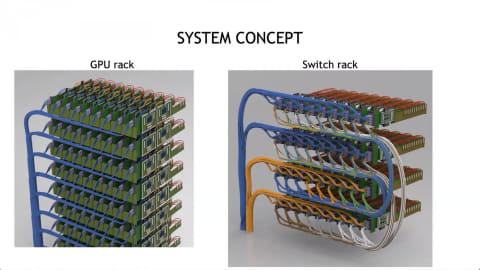

それはともかくとして、それぞれのPICからの出力はMTP Connectorに繋がり、あとはMTP Connector同士を光ケーブルでつなぐ、という形の実装になる。なんとなく明らかにSwitchの方のConnectorが足りない気はするのだが。それとLaser Sourceはカードの後ろ側に取り付ける形になっている。これを集積する構図が図06だ。

もちろん、実際にはこんな高密度での集積は不可能(そもそもGPUもSwitchも、熱伝導プレートどころかヒートシンクすらついてないので、通電した瞬間にチップが熱で死にそうだ)だが、まぁ、言いたいことは分かる。

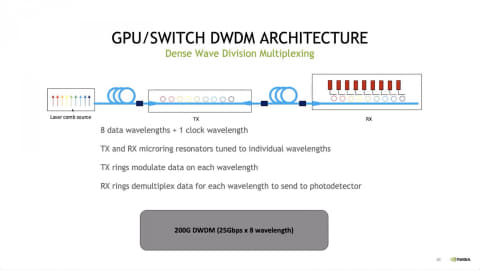

さて、肝心なのはここからだ。先にCPOをDWDMで使うという話だったが、構成はこんな感じだ(図07)。データ8本+クロックで合計9波長をLaser Sourceで生成、Micro Ring Modulatorを利用して多重化/多重分離を行う格好だ。

面白いと思ったのは、信号は25Gbpsどまりで、つまり25GT/secのNRZと思われ、8波長で200Gbps/Laneという速度になることだろうか。2022年頃だから、まだ25GT/secのPAM4だと変調/復調やエラー訂正などに結構大規模な回路となってしまうことを嫌がったのかもしれない。もう1つ理由があり、この200Gbpsという信号速度はNVLink Gen5とマッチさせるものだった。下の表はNVLinkの仕様をまとめたものである。Gen1~Gen3はSingle Ended Signalingだったが、Gen4からPAM4変調を採用した関係でDifferential Signalに変更され、なので配線数は倍増している。

| 信号速度 | 変調 | バス幅 | 転送速度(Udir) | Link数 | |

| Gen1 | 20GT/sec | NRZ | 8bit/dir | 20GB/sec | 4 |

| Gen2 | 25GT/sec | NRZ | 8bit/dir | 25GB/sec | 6 |

| Gen3 | 50GT/sec | NRZ | 4bit/dir | 25GB/sec | 12 |

| Gen4 | 50GT/sec | PAM4 | 4bit Diff/dir | 25GB/sec | 18 |

| Gen5 | 100GT/sec | PAM4 | 4bit Diff/dir | 50GB/sec | 18 |

それはともかくとして、実質的な信号1本あたりの速度は20Gbps→25Gbps→50Gbps→100Gbps→200Gbpsと世代毎にどんどん高速化しているのが判る。このGen5というのはBlackwell世代のものだが、2022年の時点ではまだHopper(NVIDIA H100/H200)世代であり、NVLink Gen4が利用されていた。なので次世代のBlackwellに採用されるGen5の信号をOpticalで置き換えることを考えた場合には、200Gbpsの信号が必要になるという判断である。

加えて言えば、WDMを使うとEthernetの場合のようにGearboxが不要である。200G Ethernetであれば25Gbps×8の電気信号を200Gbps×1に変換して送り出す(あるいは200Gbps×1を受け取って逆に25Gbps×8に変換する)必要があるが、WDMなら25Gbpsのまま送受信できるから、Gearboxが不要というメリットもある。

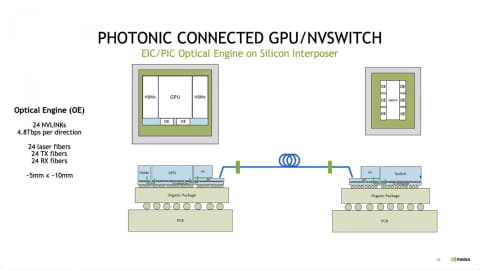

このOptical Engineを実際に搭載する想定図というのが、図08である。

GPUに2組のOE(Optical Engine)が搭載され、ここからNVLink Switchに光ファイバーで接続されるという構図だ。24本のNVLinkを搭載し(ということは、OEあたり12対24本の光ファイバーが出る計算になる)、トータルで片方向あたり4.8Tbpsなので1本あたり200Gbpsという計算になる。

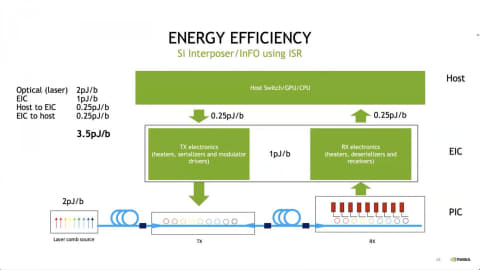

OEの大きさは5mm×10mm程度とされるので、HBMの半分くらいの体積となる。これを見ていると、OEの構造は下にPICが搭載され上にEICが載る格好で、PICにTSVが設けられ、InterposerからTSV経由でまずEICに信号が渡り、そこからPICに信号が渡されるというTSMC方式に近い。この際の必要となるエネルギーの想定値が、図09となる。

トータルで3.5pJ/bitというのは、NVLink Switchまでの伝達で考えると、かなり良い数値と考えられる。

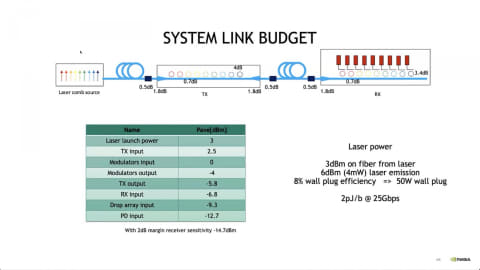

Link Budget、つまり経路での信号損失に関しての算出もあり、トータルで-12.7dBほど。そこに2dBのマージンを乗せて、PD(Photo Detector)の感度は-14.7dBあれば良いとされている(図10)。これは比較的容易に実現できる数字だし、PAM4とかならともかくNRZだったらSNRも比較的高く取りやすいので、実現への支障も少なそうだ。

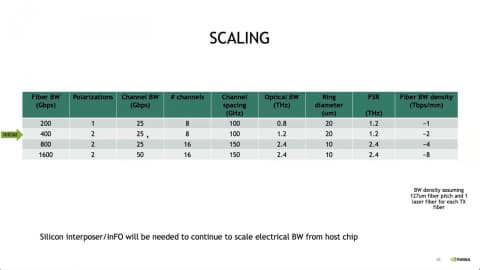

計画では今後、1600Gbps(双方向:片方向だと半分)まで転送レートを引き上げる計画になっていた。それでもギリギリまで信号速度そのものは25GT/secに留め、波長の多重数を倍増する方向を考えていたようだ(図11)。

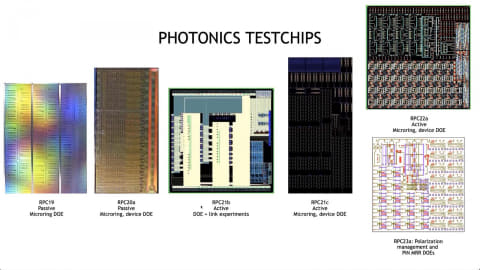

そして2022年の時点で、既にさまざまなDOE(Design of Experiments)が実施されていたことも明らかになっており、実現不可能な技術を並べていたわけではなく、それなりに確度の高い積み上げを行っていたことを伺わせる。

2025年に発表された予想外の方針転換、原因はFotonixのトラブルか?

さてここまで見てきたように、少なくとも2023年の時点まで、NVIDIAはNVLinkのOpticalへの移行を真剣に検討していたことが分かる。そして2025年にNVIDIAがまずSpectrum-XとQuantum-XにCOUPEベースのCPOを採用することを発表した時点で、「次はNVLinkだ」と予測したのは筆者だけではなかった。

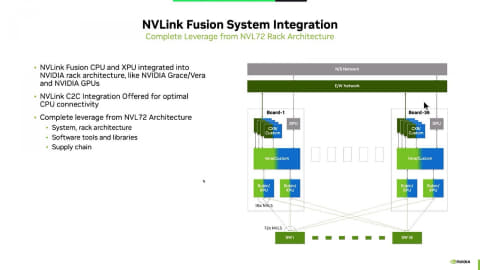

さて今年のHot InterconnectsでNVIDIAは"Building Custom AI Infrastructure with NVLink Fusion"という発表を行った(図13)。

NVLink Fusionは要するにNVLink ProtocolをNVIDIA以外でも利用できる様にするための取り組みで、具体的にはNVLink I/F Chipletを(NVIDIAが提供するのか、NVIDIAがIPを提供して顧客が製造するのかはともかく)を顧客のCPU/GPUとUCIe経由で接続する事で、「NVIDIAのCPUと顧客のXPU」あるいは「顧客のCPUとNVIDIAのGPU」といった混在環境を構築できるようにするという取り組みである。

こちらの詳細は今回の記事の趣旨から外れるので省くが、重要なのはこのNVLink Fusionも電気信号ベースになるということだ。これについて発表者であるKrishnan Geeyarpuram氏(Senior Distinguished Engineer)に"Are there any plans to switch NVLink to optical cable? Will NVLink 6 continue to use copper?"という質問を投げたところ、返事は"NVLink6 uses the same copper cabling, NVLink spine, and MGX rack architecture (named Oberon rack in our roadmaps) as Blackwell with NVLink5. The goal is to remain in copper for scale-up, for as long as we can, while still being able to meet the performance, power, and latency design goals."という事で、NVLinkは可能な限り電気信号を使い続ける方針になったことが告げられた。少なくともNVLink 6は電気信号なのは確定であり、この返事だとNVLink 7も怪しい。可能性があるとすればNVLink 8以降だろうか?

2023年から2025年の間に、どうしてここまでの方針転換があったのかは不明である。1つ可能性を挙げるとすれば、実は2022年当時NVIDIAはGlobalFoundriesのFotonixを利用していた。というのはGlobalFoundriesの2022年3月のプレスリリースによれば、Fotonixの第1世代のパートナー企業の中にNVIDIAの名前がちゃんと記されていたからだ。ここから考えると、そもそもSpectrum-XやQuantum-XがTSMCのCOUPEを利用していることが奇妙であって、ということはFotonixに何か問題があったのか、もしくはOptics以外の要因でCOUPEが選択されたのか、ということになる。

どちらにしても、Fotonixベースで推進していたと思われるNVLinkの光化には障害になった、という事なのかもしれない。結果として暫くNVLinkは電気信号のまま頑張らざるを得なくなったことそのものは間違いない。単純に電気信号→光信号に進めるわけではないという事情を垣間見る思いである。