期待のネット新技術

NVIDIA発表の「Spectrum-X」「Quantum-X」に見る、TSMCの光電融合パッケージ技術「COUPE」の詳細

Silicon Opticsの現状(6)

2025年9月2日 06:00

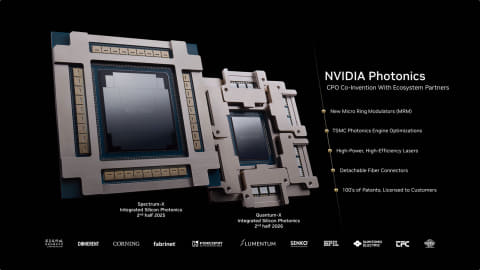

前回はNVIDIAが採用を発表したTSMCのパッケージ技術「COUPE」について取り上げた。今回はこの続きとして、COUPEおよびNVIDIAが発表しているSpectrum-X(Ethernet Switch)およびQuantum-X(Infiniband Switch)の詳細を見ていく。

NVIDIAのSwitchに搭載されるCOUPEベースのSilicon Photonics Engine

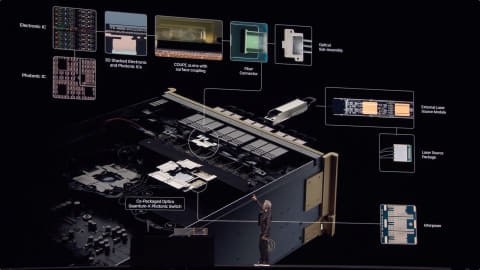

前回の図11でも示したが、NVIDIAはSpectrum-XおよびQuantum-XにCPOを搭載するとしている(図01)。ここでSpectrum-XとQuantum-Xの大きさが異なるのは、ポート数が異なるためである。ラフに言えばSpectrum-XはQuantum-Xの3倍のポート数を実装する。

ちなみに現行世代では、下表のような構成になっており、Quantum-X800は最大144ポート、Spectrum-4は最大256ポート構成となる関係で、パッケージはSpectrum-4の方が大きい。

| Switch ASIC | ポート速度×数 | Switch ASIC | ポート速度×数 |

| Spectrum-2 | 400G×16 | Quantum-1 | 200G×40 |

| 200G×32 | |||

| 100G×64 | |||

| 50G×128 | |||

| Spectrum-3 | 400G×32 | Quantum-2 | 400G×64 |

| 200G×64 | 200G×128 | ||

| 100G×128 | |||

| Spectrum-4 | 800G×64 | Quantum-X800 | 800G×72 |

| 400G×128 | |||

| 100/200G×256 |

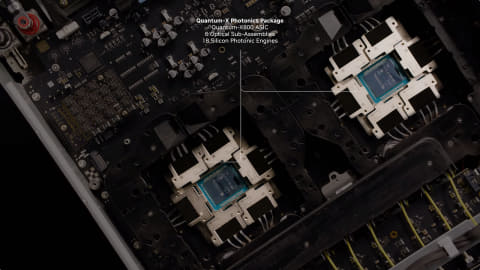

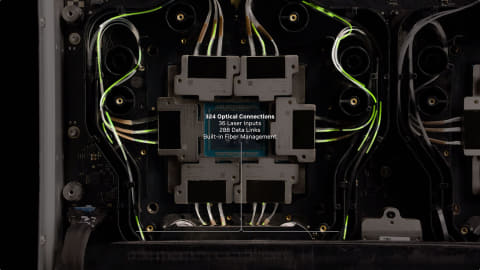

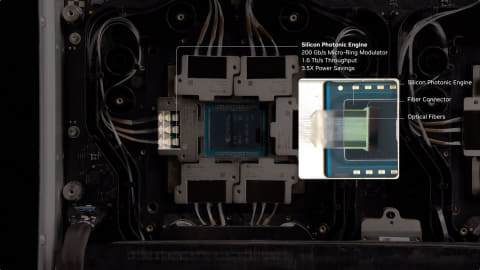

さて、そのQuantum-X800をベースとしたCPOパッケージの場合、Switch ASICの周囲に6つのOptical Sub-Assemblyが搭載され、それぞれに3つのSilicon Photonics Engineが搭載される(図02)。つまり、18個のSilicon Photonics Engineが搭載されるわけだが、ここから合計で36本のLaser Inputのほかに288本のData Linkが出るとしている(図03)。つまり、1つのSilicon Photonics Engineあたり2本のLaser Inputと16本のData Linkを持つ計算になる。

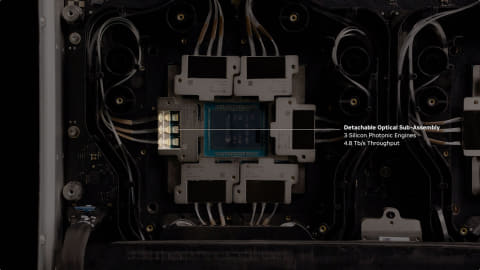

3つのSilicon Photonics Engineで4.8Tbpsのため、1つあたり1.6Tbpsであるが、Data Linkは双方向通信になるため、Data Linkは1本あたり200Gbpsとなる計算だ(図04)。ちなみにこのSilicon Photonics EngineのFiber Attachはあまり他で見かけない構造になっており、恐らくはNVIDIAがTSMCと共同開発したものと思われる(図05)。

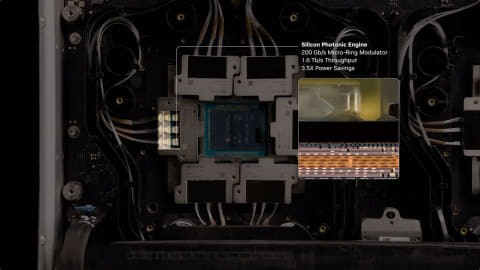

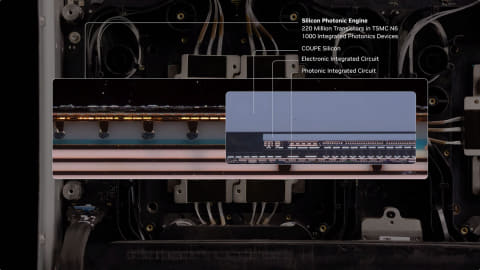

さて、肝心のSilicon Photonics Engineであるが、これは200GbpsのMicro-Ring Modulatorを持つ構造である。この中身(図06)をもう少し拡大したのが図07である。ここで明確に「COUPE Silicon」と書かれていることからも分かるように、このSilicon Photonics EngineはTSMCのCOUPEをベースとして構築されている。

出力されるレーザー光源の数とLaser Inputの数が合わない?

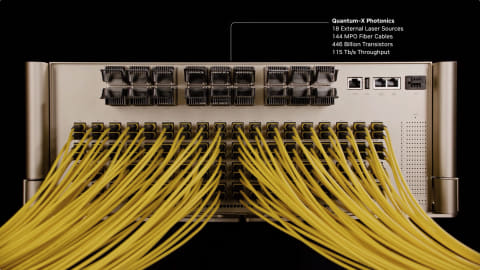

ところで、図02に戻ると、写真でいえば2つのSwitch ASICが並ぶ右下に、黄色の太めのファイバーが出ているのが分かる。ここに接続されるのがレーザー光源である(図08)。

このレーザー光源は、1つのModuleから8本出力可能とされている。ちなみにQuantum-X800全体ではこれが18 Module装着可能である。つまりSwitch ASIC1つあたり9 Moduleということになる。Switch ASICあたりでは72本のレーザー光源が提供されることになる計算なので、Silicon Photonics Engineあたり4本ということになる。つまり、4本の送信レーンに対してそれぞれ1本ずつということだが、それでは図03にあった「36 Laser Inputs」と数字が合わない。

なぜ合わないのか? 可能性として考えられるのは以下の3点だ。

- 4本のうち2本は冗長用のスペア

- 実は1波長あたり200Gbpsではなく、1波長あたり100Gbpsであり、これを2波長のWDMで多重化して送受信している

- 2本のLaser出力を1本に多重化(波長は同じ)して送り込み、Silicon Photonics Engineの中で1:2に分割して使っている

しかし、2番目はMRMが200Gbpsである必要がないので、多分×。3番目は2本の出力の同期を取るのが難しいので、これも多分×であり、おそらく1番目の理由だと思われる。それだけELS(External Laser Source)の寿命が短いという話なのだろうか? ちょっとこのあたりの事情を知りたいところだ。

COUPEに採用されている積層技術「3D SoIC」

最後に、全体の写真である(図10)。COUPEを構成するEIC(Electronic IC)とPIC(Photonic IC)の製造、それの3D積層とMicroLensの構成あたりまでは、おそらくTSMCだ。ただそれ以外の部分はどこで製造を行っているかは不明である。

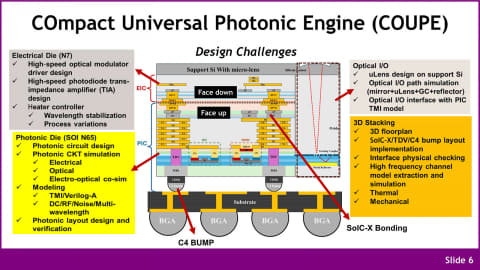

さて、ここで話がTSMCに戻るのだが、2025年6月のVLSI SymposiumでTSMCはCOUPEの詳細な構造を公開した(図11)。TSMCのReferenceではEICをN7プロセスで、PICをSOI N65プロセスでそれぞれ製造する。今回NVIDIAはEICこそN6プロセスと明示したが、PICの方は何も説明がないあたりはSOI N65プロセスでの製造のままと思われる。

さて、TSMCはこのCOUPEを3D SoICと呼ばれる方法で接続している。通常、半導体チップの実装にはBumpと呼ばれるハンダのballを利用する(図11で一番下にあるC4 Bumpや、PICとSubstrateの間に入っている小さなC4 Bumpがそれだ)。これはハンダなので、リフロープロセス(基板とチップ全体に熱を掛け、ハンダを溶かす工程)を経て基板に密着する事になる。

ただ密着といっても、それは人間の目から見ての話で、顕微鏡を見ると数十μmの厚みのハンダの両側に銅の配線がくっつく形になっているわけだ。ハンダは昔だとスズと鉛ベース、今だとスズと銀・銅の合金で構成されるが、これと銅配線の接合部に抵抗が生じることになる。前回の記事の図04や図05は、単に配線だけの問題ではなく、この配線の接合部にBumpを使うことで特性が悪化するというものである。

なので間に余分な金属を挟まずに直接銅配線同士を接続することで性能の低下を防ごうというのがSoIC(System on Integrated Chips)という技法である。もっとも単に乗せただけでは、間がつながっていることにはならない。

積み木を2つ積んでもすぐにずれてしまうため、これをずれないようにするためには両面テープなり接着剤を使うのが普通で、ハンダはまさしくこの両面テープというか接着剤的な役割を果たしていた。SoICではこうした接着剤の代わりにファンデルワールス力(その中でもファンデルワールス吸着と呼ばれる原理)を利用する。2つの接触面を極めて均一にならして接続すると、間にファンデルワールス力が働いてしっかり結合するという物理現象である。

これを利用するためには、本当に接続面を均一にする(正確な数字は公表されていないが、nmオーダーではまだ粗すぎるかもしれない)必要があり、技術的難易度は高い。TSMCはこれを利用して複数のチップを3次元的に積層するサービスを以前から提供しており、AMDなどが採用して既に商用チップを多数出荷しているが、COUPEでもこれを利用してPICの上にEICを載せている格好だ。このCOUPEで信号を出力する場合、以下の過程を取る。

- 外部(この例で言えばQuantum-X ASIC)からの信号をBGA C4 Bump/UMBM C4 Bump経由で左側のTSV(Through Silicon VIA:貫通シリコン電極)を経由してPICの中を素通りさせ、EICに送る。

- EICは必要な処理を行って、元々のデジタル信号を光変調のための信号に変換し、右側のTSV経由でPICに送り込む。

- PICに入った信号はMRM(Micro Ring Modulator)に渡され、ここで光の変調が行われる。元々MRMにはELSから連続レーザー光が入っており、MRMは渡された信号に基づきこのレーザー光の変調(NRZなら0か1の2段階、PAM4なら0/1/2/3の4段階に出力を加減する)を行う。

- MRMから出た変調後の光は、PICの中の導光路(図11で薄い水色の部分)を通り、一番右のGrating Couplerと呼ばれるところに導かれる。これと、その下にあるMetal Reflectorにより光が上方に送り出される。

- Grating Coupler/Metal Reflector上方に位置するシリコン製のMicroLensにより焦点を合わせるなどしたうえで、Fiber Attachに光が送り出される。

受信というか受光の場合はこれが逆になり、MRMの代わりにPD(Photo Detector)が送られてきた光を受信する。その出力がEICに送られ、EIC内に置かれたTIA(Transimpedance Amp:PDの出力は電流値になるので、これを電圧値に変換することで扱いやすくする回路)を経由して、またTSV→C4 Bump経由でQuantum-Xに送り出されるというわけだ。

さて、NVIDIAに話を戻すと今回のSpectrum-X/Quantum-XはそれぞれEthernet/InfinibandのSwitchであるが、NVIDIAの本命はNVLink/NVSwitchの光化である。次回はこれについて説明したい。