期待のネット新技術

NVIDIAが採用を発表、TSMCが開発した光電融合パッケージ技術「COUPE」

Silicon Opticsの現状(5)

2025年8月5日 06:00

本シリーズの第2回、第3回で取り上げたBroadcom、第4回で取り上げたMarvellは、それぞれ自前でSilicon Photonicsのソリューションを開発し、これを自社で利用するとともに、Design Serviceのかたちで提供もしている。

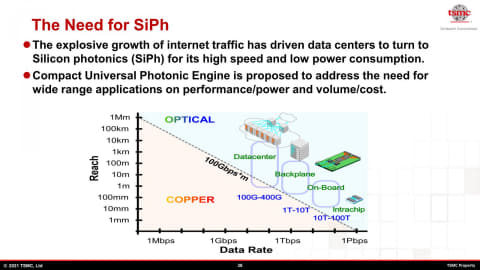

では、自社製品が存在しないPure Foundry(ピュアファウンドリー:100%顧客の製品だけを製造する)はどうか? ということで、最も代表的なメーカーがTSMCである。同社は、2021年のHot ChipsのTutorial Sessionの中で、Silicon Opticsが今後必要になることを説明した(図01)。

ちなみに、従来型のOpticsでは何故だめかという説明は省略されたのだが、これは主にコストと実装面積の点から説明できる。

従来であれば、発光/受光素子はIII-V族半導体(発光ならGaAsやGaP、GaNなど、受光ならInGaAs系)を利用して製造し、あとはMicroLensの類や、必要ならWDM用の部品(MUX/DEMUX)はガラス系あるいはプラスチック系素材をベースに構築して組み合わせるかたちだった。

これはPluggable Transceiver Moduleに組み込める程度には小型化されており、かつ値段もこなれているわけだが、言い換えると、最低でも1個$100程度のPluggable Transceiver Moduleだから許容されるという話でもあり、また大きさもSwitchとかEthernet I/F Card向けには十分であっても、Chip-to-Chipなどを接続するには大きすぎる。

特に量産を考えた場合、CMOSプロセスと親和性のない既存の送受光素子を組み込むというのは、後工程で基板の上にDiscrete部品として実装するかたちになるので、それだけコストも上がるし高密度の実装が難しい。

できれば基幹部品に関してはCMOSプロセスのかたちで製造できればコストも下がるし高密度化も容易になり、長期的には既存のASICの中に組み込むことも可能になる「かもしれない」。

先端ASICへの光回路統合は困難

実は、2000年くらいにSilicon Opticsの開発が始まったときの各社のロードマップは、既存のASICにSilicon Opticsのかたちで光送受信回路を統合することを強く意識していた。ただ、その後開発が進んでいく中で、どうにもこれは難しいということが次第に明らかになってきた。Silicon Opticsは確かにCMOSベースのロジック回路と親和性のあるかたちで基幹部品を構築できるが、必ずしも最先端のロジック向けプロセスというわけではない。

例えば、本シリーズ第1回でIntelのロードマップというか基幹コンポーネントについて紹介したが、CMOSベースのTIAは22nmでの製造となっている。2022年といえば、すでにIntelは10nmプロセスをベースにしたIntel 7の量産準備を始めていたころで、22nmプロセスは2世代遅れになっている。

どういうことかというと、次の2点の問題がある。

1点目は開発サイクルの問題だ。先端プロセスは当然ながら電気信号ベースのロジック回路を構築することを目的に開発されており、かつ競争が激しい分野なので次世代・次々世代のプロセスに向けて微細化や高速化・量産の安定化などに開発リソースは集中している。Silicon Optics向けの開発は、なのでそのプロセスが安定して量産できるようになってから、そこにアドオンのようなかたちで行われることになるので、常に最先端から数世代遅れにならざるを得ない。

2点目はコストの問題だ。特に14nmあたりから先端プロセスを利用する際の製造コストが急騰しており、その一方でOptics周りに関してはいわゆる微細化の恩恵をそれほど受けない。どういう話かといえば、40nmプロセスで作ろうが7nmプロセスで作ろうが、Opticsのコンポーネントの寸法はほとんど同じである。ロジック回路の場合、製造コストこそ上がるものの実装密度と性能も上がる関係で、同じ回路を微細化する、とそのぶん小型化・高性能化(ないし小型化・省電力化)できる。そのため、製造コストの上昇分をある程度相殺できるが、Opticsに関してはこれが全く期待できない。なので、最新プロセスを使っても無駄にコストが上がるだけである。

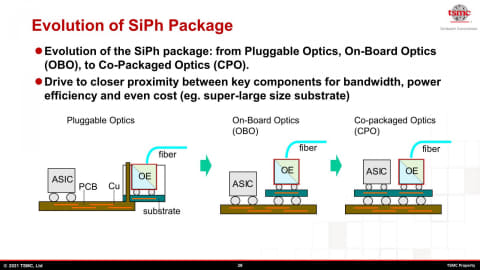

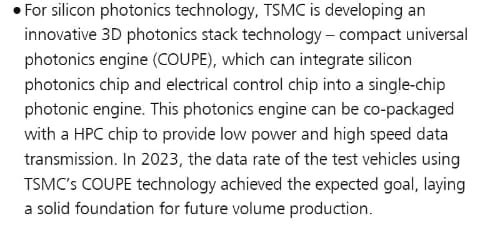

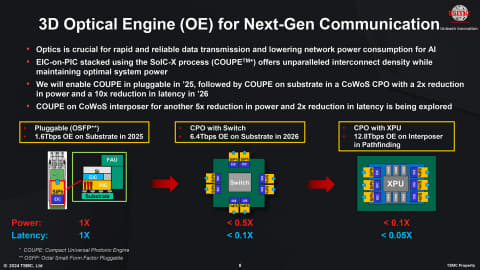

TMSCの説明では、このあたりを省いた上で、OE(Optical/Electrical)の部分をASICとは別に構築することを前提にして、3種類の構成を示している(図02)。TSMCはこの左から右に向けて、順次ソリューションを提供していくかたちである。

ただ、このTutorial Sessionの目的はOEの位置ではなくOEの中身の方である。

2021年、EICとOICを3D積層する新パッケージ技術「COUPE」試作

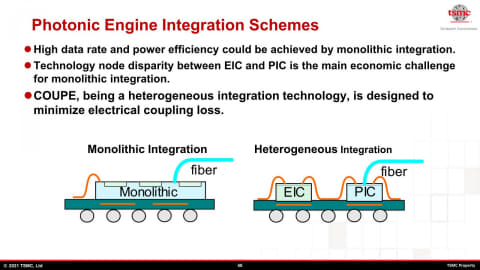

OEも単純に言えばMonolithic構成と、EIC(Electrical IC)/OIC(Optical IC)を別々にしたHeterogeneous構成がある。ここでMonolithicというのは今説明していた、EICとOICを同一のSiliconで構築しようという方式で、技術的にもコスト面でも難易度が高い。

ここで言うEIC、Pluggable Transceiver ModuleのEthernetであれば単に電気/光の変換のための回路だけでなく、その前段のDSPとかも含まれることになるが、このDSPの実装には最先端プロセスが要求されるから、Monolithic構成は非現実的である。なのでHeterogeneous構成を選ぶのは必然ではあるのだが、そこに向けてTSMCが(この時点では)開発中だったのがCOUPEである。

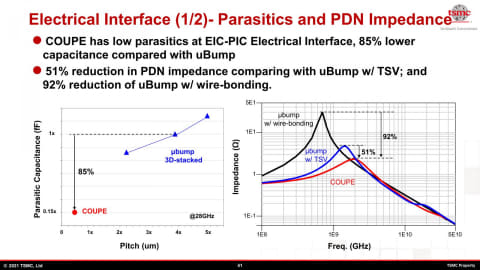

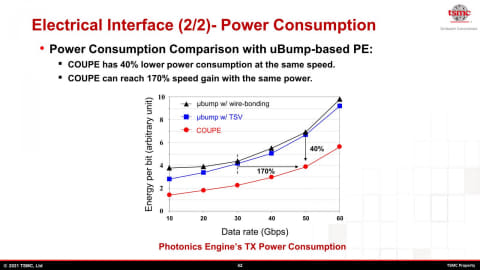

COUPEはCOmpact Universal Photonic Engineの略であるが、実はこの時点ではまだ具体的な構造などは公開されていない。ただCOUPEを使うことで寄生容量を減らし、インピーダンスも低めにおさえられ(図04)、そのためデータ転送に要する電力そのものを減らせる(図05)としている。

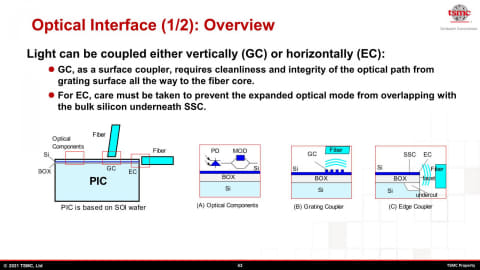

PICの製造方法が、図06だ。SOIウェハの上にOptical Componentを構築し、そこから光ファイバー用のコネクタ部を構築するかたちだが、垂直方向(GC)と水平方向(EC)のどちらにも構築が可能、としている。

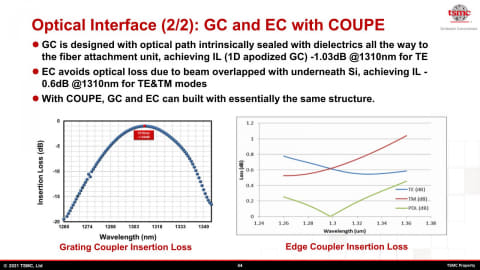

この2021年の試作では、1310nmあたりの光をターゲットとしており(図07)、挿入損失も低くおさえられるとしていた。

2024年、目的の性能を達成したCOUPEの提供始まる

この2021年の話は、「この当時TSMCが取り組んでいる将来のパッケージ技術」という括りであり、ほかにもISMC(Integrated Si Micro-Cooler:パッケージ内の冷却技術)なども紹介されていて、「実現時期は定かではない将来」的な扱いであった。

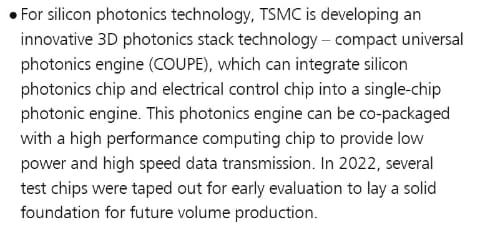

ただその後、2022年のAnnual Report(図:08)には複数種類のテストチップのテープアウトを2022年中に行って評価を開始していることが示され、また2023年の"5 Operational Highlights"(図09)ではそのテストチップを利用して、目的とする性能が出たことが示されている。

そして2024年に入り、4月の米国を皮切りに北米とヨーロッパ、台湾、中国と回って6月末の日本で締めくくられたTSMC Symposium 2024ではCOUPEがFoundryとして顧客に提供できるオプションになったことが示された。

2025年には1.6Tbps(これが100Gbps×16なのか200Gbps×8なのか、あるいは50Gbps×32なのかは不明)のCOUPEが構築可能であり、2026年には6.4Tbps、その先には12.8Tbpsを目指すが、12.8Tbpsに関してはInterposerの方がまだPathfinding(技術的に可能な方法を探求する)段階なのだそうで、当面は2026年の6.4Tbpsを目指すことになる。

このスライドで、TSMCはEICとOICを、SoIC-Xと呼ばれる同社の3次元積層技術(μBumpを使わずに、直接VIA同士を接続する方式)で構築するとしている。物理的には、PICが一番下になり、その上にひっくり返したことでEICのダイが載ることになる。

また、配線層(Substrate)とEICの間にもVIAが設けられている。そのため、信号は配線層→VIA→EIC→PIC→FAU(送信の場合。受信は逆)という順に流れることになる。

図10のスライドでは穏当に、まずはPluggable Transceiver Module向けに実装といったロードマップが示されていたが、実はこのマーケットは大変に競争が激しい部分でもあり、既存の主要なベンダーは自前でSilicon Photonicsを実装しているか、もしくはSilicon Photonicsと十分価格競争力のあるDiscreteのソリューションを用意してこれを製品化して投入している。Discreteであっても数が出れば量産効果で価格が下がるから、ここでちょっとだけSilicon Photonicsを入れたからといって劇的に価格が下がるということにはならない。結果として、公開されている中で最初にCOUPEを導入したのはNVIDIAとなった。

2025年、NVIDIAが次世代スイッチへのCOUPE採用を発表

2025年3月に開催されたGTC(GPU Technology Conference)において、NVIDIAはSpectrum-X及びQuantum-Xと呼ばれるNetwork Switchを発表した。もっと正確に言えば、Spectrum-X(Ethernet Switch)やQuantum-X(Infiniband Switch)はもう2023年頃から発表されているデータセンター向けのSwitchであり、例えば最新版であるSpectrum-4はポートあたり最大800Gbps、スイッチング速度51.2Tbps(つまり800G×64ないし400G×128/200G×256)のスイッチング性能を持っている。このSpectrum-4を搭載した製品としてはSN5600及びSN5400の2製品が存在する。

ただ、Spectrum-4はあくまでも電気信号ベースのSwitchなわけだが、GTCで発表されたのはこのSpectrum-4の次世代製品にTSMCにCOUPEを利用したCPOの構成を取ることで、直接光信号を出せるようにした、というものだ(図11)。次回は、このNVIDIAのSwitchの内部を、もう少しご紹介したい。