期待のネット新技術

光電融合のもう1つのキープレイヤー、TSMCに対抗するGlobalFoundriesの「Fotonix」

Silicon Opticsの現状(8)

2025年11月4日 06:00

今年4月から、「Silicon Opticsの現状」シリーズとして、さまざまな企業がSilicon Opticsに向けて技術あるいはソリューションを提供すべく開発を続けていることを紹介してきた。

最初のNTTとIntelは、以前からこの分野にAddressすることを公言し、実際に取り組んできたという意味で最初に取り上げた。また10月にIOWN 2.0が発表されたため、こちらの紹介も番外編として行った。

しかし、ことNetworkの分野においては、BroadcomとMarvellという2大Switchベンダーというか、Network関係ソリューションベンダーがやはりSilicon Opticsに前向きなのは当然であり、そんな理由からこの2社を続けて取り上げた。ただBroadcomにしてもMarvellにしてもFabless企業であり、製造は外部に委託せざるを得ない。それを受託しているのがTSMCであり、同社はCOUPEというSilicon OpticsというかCPOのソリューションを提供している。

Broadcom/MarvellはこのCOUPEを使わずに自力でCPOを提供しているあたりが他社との違い、ということになるが、一方でそのCPOを素直に使ったのがNVIDIAである。ここで説明するまでもなく、NVIDIAは現在のAI向けデータセンターで圧倒的ともいえるシェアと売上を確保しているベンダーだ。

そのNVIDIAがデータセンター内のネットワークとしてCPOを利用したOptical Interconnectを予定しており、それがTSMCのCOUPEベースという話になっているわけだが、一方で、それ以前に予定されていたNVLinkは引き続き銅配線ベースでの接続になる、というのが、前回までの概略となる。

これまでの「Silicon Opticsの現状」

- ネットワーク・コンピュータの双方で進む光信号化の取り組み―NTT「IOWN」構想とIntelのロードマップを見る

- Broadcomが先導する、光電融合のキーテクノロジー「CPO」の先進性と課題

- Broadcomが量産を進める「CPO」が背負う期待、一方、その欠点はどのように対策されるか?

- MarvellのSilicon Photonics~光源の外部配置や「2.5D」構造など独自のアプローチも

- NVIDIAが採用を発表、TSMCが開発した光電融合パッケージ技術「COUPE」

- NVIDIA発表の「Spectrum-X」「Quantum-X」に見る、TSMCの光電融合パッケージ技術「COUPE」の詳細

- NVIDIAのGPU間データ伝送技術「NVLink」に見る、電気→光の移行が一筋縄では行かない例

- NTTが発表した「IOWN 2.0」を、ちょっと深堀りしてみる(番外編)

NVIDIAとNVLinkに関する補足

そういえば先月は軽く流してしまったが、NVIDIAのGPUに詳しくない読者のために補足しておくと、NVLinkはGPU同士を接続するInterconnect、Connect-XやQuantum-Xはシステム同士を接続するInterconnectとなる。実はNVLink、第1世代については最大で8枚のGPUを相互接続するためのLinkでしかなかった。8枚のGPUカードと2つのCPUをPCIe Switchで繋ぎ、この全体を1つのシャーシに纏めるという仕組みで、要するにシャーシ内の接続用という位置づけである。

これが第2世代では、GPUの相互接続用という位置づけと接続枚数の8枚は変わらないものの、GPU-(NVLink)-GPUという第1世代方式からGPU-(NVLink)-NVSwitch-(NVLink)-GPU、という仕組みになった。要するに、間にNVLink専用Switchが挟まった格好だ。第1世代だと、特定の接続だけ帯域を増やすといったことはできないが、間にSwitchを挟むことで、このあたりの柔軟性が増した格好だ。Linkの速度と本数も増えたことで、絶対的な帯域も増えた(もっともその分Latencyも増えたが)。

第3世代も性能こそ上がったが、第2世代の延長にある。変わったのは第4世代で、Hopper GPUにGlace CPU(中身は72coreのNeoverse V2)の接続にNVLinkを利用するようになったほか、Hopper GPU同士も最大256 GPUまでの接続が可能になっている。要するに256枚のGPUで1つのクラスタ(NVIDIAはこれをSuperPODと呼んでいる)を構成するが、このクラスタ内はNVLinkで接続。そしてクラスタ同士の接続をEthernetないしInfiniBandで繋ぐという形になる。

厳密に言えば、NVLinkはEthernetとは別の扱いになるので、Ethernetを利用した通信などをNVLinkには通せない関係で、1つのSuperPod内に含まれるCPU同士はNVLinkとは別にEthernetを利用して接続されているが、こちらは通信量がNVLinkよりずっと少ない(少なくともGPU同士のデータの同期には使われない)ので、これは無視して良いかと思う。NVLinkとEthernet/InfiniBandの使い分けというか使われ方の違いはこんな感じである。

「Fotonix」は、PICとEICを統合していることが特徴

さて話を元に戻そう。そんなわけでNTT/Intel・Broadcom・Marvell・NVIDIAの各社のソリューションを7回ほど紹介してきたが、もう1つ欠かせない大物がある。それがGlobalFoundriesである。

GlobalFoundriesは2018年に、Silicon Photonicsの分野に参入することを発表した。実はもうこの時点でいくつかの基幹部品の開発は完了しており、同社の90nm SOI RFプロセスの上でこれの提供をスタートしたと発表している。ただこの時点ではまだ「いくつかの基幹部品」の提供にとどまっており、包括したソリューションには至っていない。

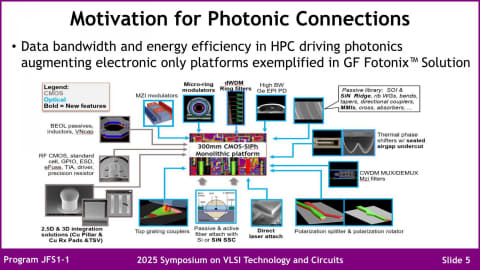

この状況を改善し、包括的なプラットフォームとしてFotonixを発表したのは、2022年3月のことである。図01がこのFotonixプラットフォームで提供されるさまざまな光学部品であり、光源以外のほぼ全ての必要となるコンポーネントをFotonix上で構築可能である(光源はTSMCのCOUPEなどと同様、外部から導入する方式)。

このFotonixの最大の特徴は、PICとEICを分離して製造する必要がないことである。先に2018年の時点で90nm SOI RFプロセス上でいくつかの部品の提供を開始していると書いたが、このプロセスで製造したテストチップは30GHzの帯域を持ち、120kmの距離を800Gbpsで繋ぐことが可能とされた。

要するに、おそらくはDWDMベースの光Ethernet(Coherentではなさそう)用のチップを製造できたという話であるが、この際にもEICをやはり同じ90nm SOI RFプロセス上に集積している。図01で言うなら水色が光学部品、グレーが電子部品になるが、RF CMOSのスタンダードセルに加えてTIAとかドライバーなどもやはり同じダイに集積可能である。要するにTSMC方式と異なり、PICとEICの接続に悩む必要がないわけだ。

この第1世代のFotonix、プレスリリースにはBroadcom/Cisco Systems/Marvell/NVIDIAといった大手メーカーに加え、スタートアップのAyar Labs/Lightmatter/PsiQuantum/Ranovus/Xanaduの各社も名前を連ねている。大手メーカーの方は説明は要らないとして、スタートアップ各社を簡単に紹介すると、次のようになる。

- Ayar Labs:Package to PackageのOptical Interconnect向けChipletを開発中

- Lightmatter:当初はOpticalベースのAIプロセッサーの開発を行っていたが、最近はOptical Backplaneの開発がメイン

- PsiQuantum:Quantum Computerを開発中

- Ranovus:Package to PackageのOptical Interconnect向けChipletを開発中

- Xanadu:Silicon Photonicsを利用したQuantum Computerを開発中

各社ともOptical InterconnectないしQuantum Computer向けであるが、Quantum ComputerにしてもSilicon OpticsでComputing Elementを開発というよりはそのチップの入出力をOptical Interconnectで実装するためにFotonixを利用しているという感じで、その意味では各社Optical Interconnectの実装にFotonixを選んだ格好だ。

実装密度を向上させた第2世代を発表

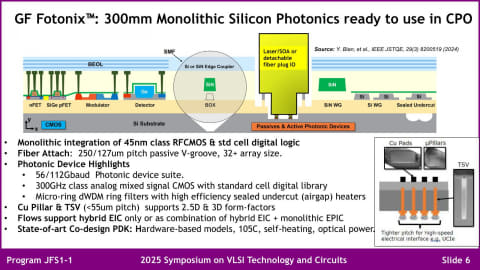

そんなFotonixであるが、2025年3月に第2世代を発表した。今回のスライドは主にこの第2世代が中心となる。最大の違いはベースとなるプロセスが90nm RF SOIから45nm RF SOIに変更されたことだ。これにより性能と実装密度の向上が図られるようになったとしている(図02)。

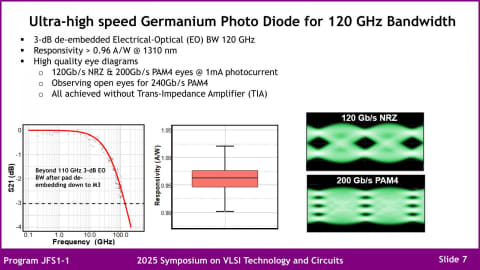

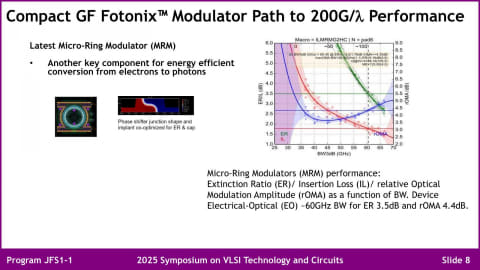

肝心の光信号の送受信性能だが、まずPhoto Diodeは120Gbps NRZ/200Gbps PAM4のどちらのケースでも十分なSNR比と受信感度を備えているとしており(図03)、送信側ではMRMを利用した変調器も200Gbps/λに対応できる(図04)としている。また内部の導光路の構築に関しても、SiベースからSiNベースにすることで、当初は4dB/cm近かった損失が、0.3dB/cm未満まで削減できたとしている。

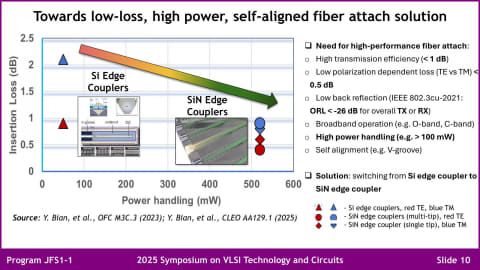

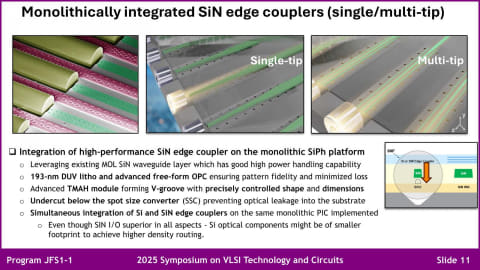

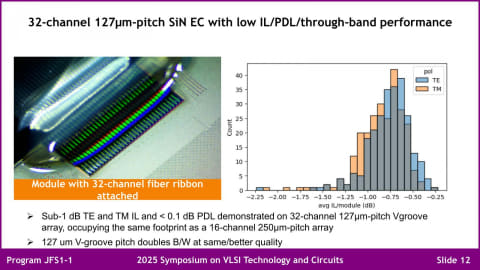

外部の光ファイバーと接続するためのFiber Attachに関しても、当初のものに比べて1dB前後の損失削減が可能になっており、特に最新のものは500mWを超える出力のサポートが可能になったとする(図06)。特にこの接続部を、通常のCMOSのプロセスを利用して構築できる(ので精度が高い)というのは、わざわざスライドを別に用意するほど(図07)大きなメリットと同社は説明する。

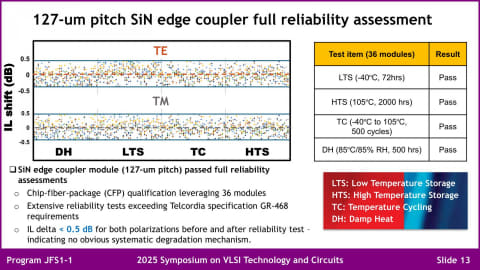

実際に32本のFiberを127μmピッチで並べた場合の特性は、250μmピッチで16本並べた場合と同等以上の特性で、帯域を倍増できるとしている。信頼性試験の結果(図08)も良好で、挿入損失のシフトは±0.5dB以内に収まっているとされる。

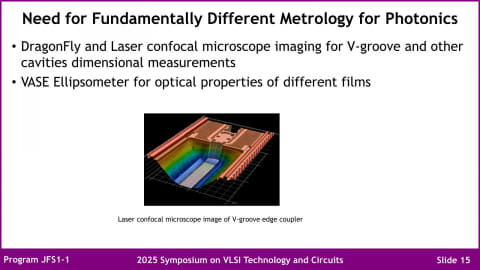

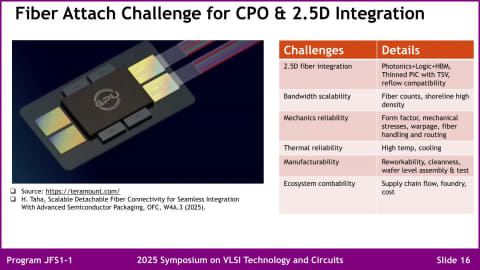

ただ同社が現在問題としているのが、DetachableなFiber Attachment部分の計測方法だ(図09)。要するに、従来と比べて圧倒的に微細な構造であるため、正しくFiber Attachment部の計測を行いにくいのだという。

また、同社は標準的なFiber Attachのための仕組みは提供していない。図10のように直接Fiberを接続してしまうと、例えば故障した場合にはFiberごと全部交換ということになる。もちろん、そうした使い方で差し支えない用途もあるが、普通はFiberをDetachableとする方が使い勝手は向上する。

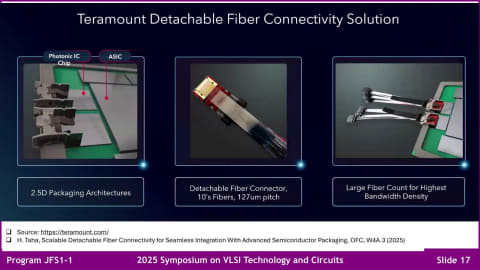

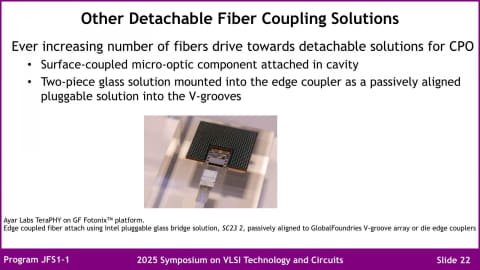

これに関しては、3rd PartyというかFotonixのエコシステムパートナーが提供する、という形に割り切っているらしい。1つの例がTeramountの提供するUniversal Photonic Couplerで、SoCのパッケージから外部にFiberを引き出せるようにするためのものである(図11、図12)。別の例としては、AyarLabsの提供するTeraPHY(図13)があり、多分今後もいくつかソリューションは出てくるだろう(LightmatterのPassageもこれに含まれる)。

全体としてみれば、TSMCのCOUPEと同等以上のソリューションを既にFotonixは提供できている格好だ。ただメリットでもあり、デメリットでもあるのがEICとPICが同一のダイであることだ。

なので、EICに複雑なロジック回路を入れようと考えた場合には、Fotonixでは色々足りないことになる。その一方、純粋なCPOだけでよければCOUPEよりも安価にシステムが構築可能だろう。

GlobalFoundries自身はこのFotonixにかなり自信を持っており、実際今年1月にはニューヨークに新しいAdvanced Packaging and Photonics Centerの開設を発表、6月にはニューヨーク州及びバーモント州の設備での半導体およびパッケージング製造能力向上のため、160億ドルの投資を発表した。このパッケージング製造能力には勿論Silicon Opticsも含まれている。TSMCに負けない巨大なSilicon Opticsの製造能力をGlobalFoundriesは提供可能にしつつある。